## Cascaded Multilevel Inverter With Series Connection of Novel H-Bridge Basic Units

K.Vijayabhaskar<sup>1</sup>, K. Bhanu chandar<sup>2</sup>

1(Assistant professor, EEE, SVPCET,I ndia) 2(Student, EEE, SVPCET, India)

**Abstract:** A new single-phase cascaded multilevel inverter based on novel H-bridge units is proposed. In order togenerate all voltage levels (even & odd) at the output, nine different algorithm-s are proposed to determine the magnitudes of dc voltage sources. Then, the proposed algorithms are compared to investigate their advantages and disadvantages. This topology is able to increase the num-ber of output voltage levels by using a lower number of power electronic devices such as switches, po-wer diodes, driver circuits, and dc voltage sources, that lead to reduction in installation space and cost of the inverter. In addition, in the proposed cascaded multi-level inverter, not only the number of requi-red power electronic devices is reduced, but also the amount of the blocked voltage by switches, and t-he number of different voltage amplitudes of the used sources is decreased. The operation and performances of the propose-d topology with its presented algorithms in generating all voltage levels have been verified by using the experimental results of a 49-level single-phase inverter.

Index Terms: Cascaded H-bridge, multilevel inverter. multileve inverter, developed

#### INTRODUCTION

Now a days, the multilevel inverters have received much attention because of their considerable advantages such as high power quality, lower harmonic components, better electromagnetic consistence, lower dv/dt, and lower switching losses. There are three main types of multilevel inverter ers: diode clamp multilevel inverter, flying capacitor multilevelinverter, and cascaded multilevel inverter. The cascaded multilevel inverters have received special attention due to the modularity and simplicity of control. The cascaded multilevel inverters are mainly classified into two groups: 1) symmetric, with equal magnitude for the dc voltage sources; and 2) asymmetric, with different values of the dc voltage sources. By increasing the magnitude of dc voltage sources, the higher number of output levels will be generated. Therefore, the asymmetric cascaded multilevel inverters increase the number of output levels by using power semiconductor devices that are the same as the symmetric ones.

now, different topologies with several algorithms to determine the magnitude of their dc voltage sources have been presented in the literatures. In the H-bridge cascaded multilevel inverter with two different algorithms as symmetric and asymmetric inverters has been presented. Two other symmetric cascaded multilevel inverters have been also presented in and. The main advantage of these inverters is the low number of different voltage amplitudes of the used dc sources. However, the higher number of required insulated gate bipolar transistor (IGBTs), power diodes, and driver circuits in generating aspecific output level are their remarkable disadvantages. In order to increase the number of output levels with a lower number of power semiconductor devices, different asymmetric cascaded multilevel inverters have been presented .The bidirectional power switches have been used in these topologies. Each bidirectional power switch includes two IGBTs, two power diodes, and one driver circuit if the common emitter configuration is used. Therefore, in these topologies, the installation space and total cost of the inverter increase. As a result, several asymmetric cascaded multilevel inverters have been presented in which the unidirectional switches from the voltage point of view and the bidirectional switches from the current point of view are used in them. Each unidirectional switch consists of an IGBT with an antiparallel diode. Two of these topologies have been presented. Two other algorithms for the H-bridge cascaded multilevel inverter have been also presented. Because of the asymmetric topology and used unidirectional switches, it seems that the lower number of power electronic devices is the main advantage of these inverters. However, the main disadvantage of the asymmetric topologies is the lost of modularity, which means the use of a high variety of semiconductor devices and dc voltage sources.

In this paper, a new single-phase cascaded multilevel inverter with series connection of the novel H-bridge basic units is proposed. Moreover, nine different algorithms to determine the magnitude of dc voltage sources are proposed to generate all output voltage levels. These algorithms are compared to each other from the number of required IGBTs, dc voltage sources, and different voltage amplitudes of the used source points of view. These investigations are done to determine the best proposed algorithm. Then, the proposed topology with its best proposed algorithm is compared to the conventional topologies. These comparisons consist of the

amount of the blocked voltage by switches and the number of used power electronic devices. Finally, in order to reconfirm the correct performance of the proposed cascaded multilevel inverter and its algorithms in generating all voltage levels, the experimental

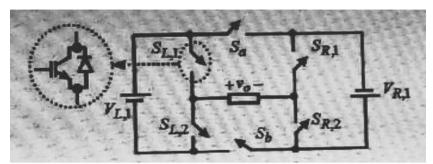

Fig. 1. Basic unit based on developed H-bridge.

| State | $S_{L,1}$ | $S_{L,2}$ | $S_{R,1}$ | $S_{R,2}$ | Sa | $S_b$ | v <sub>o</sub>      |

|-------|-----------|-----------|-----------|-----------|----|-------|---------------------|

| 1     | 1         | 0         | 0         | 1         | 0  | 1     | $V_{L,1}$           |

| 2     | 0         | 1         | 1         | 0         | 0  | 1     | $V_{R,1}$           |

| 3     | 1         | 0         | 1         | 0         | 0  | 1     | $V_{L,1}+V_{R,1}$   |

| 4     | 1         | 0         | 1         | 0         | 1  | 0     | 0                   |

|       | 0         | 1         | 0         | 1         | 0  | 1     | V                   |

| 5     | 0         | 1         | 1         | 0         | 1  | 0     | $-V_{L,1}$          |

| 6     | 1         | 0         | 0         | 1         | 1  | 0     | $-V_{R,1}$          |

| 7     | 0         | 1         | 0         | 1         | 1  | 0     | $-(V_{L,1}+V_{R,1}$ |

Table I Output Voltage Of The Developed H-Bridge Topology Based On Different Sitching Patterns

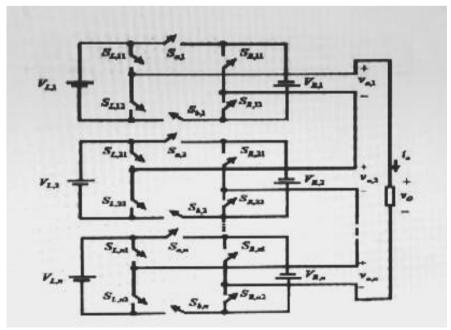

Fig. 2. Proposed cascaded multilevel inverter.

inverter is shown in Fig. 2. According to Fig. 2, the output voltage of the proposed cascaded multilevel inverter is equal to adding the output levels of different units and is given by results of a single-phase 49-level inverter based on the proposed topology are used.

## PROPOSED TOPOLOGY

The topology of the novel H-bridge basic unit is shown in Fig. 1. This unit consists of six unidirectional power switches from the voltage point of view (SL,1, SL,2, SR,1, SR,2, Sa, and Sb) and two insulated dc voltage sources (VL,1 and VR,1), which is called the developed H-bridge unit [22]. The main disadvantage of the proposed basic unit over the H-bridge is its higher number of required dc voltage sources and power switches; however, this basic unit is able to generate seven different levels at the output, whereas three output levels are only generated in the H-bridge. Table I shows the generated output voltage levels based on the different switching patterns in the proposed basic unit. In this table, 1 and 0 indicate the on and off states of the switches, respectively. As shown in Table I, this basic unit is able to generate seven levels (three positive levels, three negative levels, and one zero level) at the output In addition, in each switching pattern, one power switches from each leg (SL,1 or SL,2), (SR,1 or SR,2), and Sa or are turne on simultaneously. If the magnitudes of the dc voltage sources are equally considered, the proposed inverter can generate five levels at the output. Therefore, in order to generate more numbers of output levels at the output, the magnitude of dc voltage sources have to be selected differently. Therefore, the

magnitude of the dc voltage sources is considered as follows:

•

$$VR,1 = Vdc$$

eq. (1)

•  $VL,1 = 2Vdc$ . eq. (2)

•  $vo(t) = vo,1(t) + vo,2(t) + \cdots + vo,n(t)$ . eq. (3)

The generated output voltage levels based on the different switching patterns are shown in Table II. In this table, 1 and 0 indicate the on and off states of the switches, respectively.

In the proposed cascaded multilevel inverter, the number of switches (Nswitch ), IGBTs (NIGBT ), driver circuits (Ndriver ), and dc voltage sources (Nsource ) are calculated as follows:

The other main parameter in calculating the total cost of the inverter is the maximum amount of the blocked voltage by switches. If the values of the blocked voltage by switches are reduced, the total cost of the inverter decreases [9]. Therefore, in order to calculate this index, it is necessary to consider the amount of the blocked voltage by each of the switches. According to Fig. 2, the values of the blocked voltage by switches SR,1 and SR,2 are equal to

•

$$VSR,1 = VSR,2 = VR,1$$

. eq. (6)

In (6), VSR,1 and VSR,2 indicate the values of the blocked voltage by switches SR,1 and SR,2 , respectively. The value of the blocked voltage by switches SL,1 and SL,2 is equal to

•

$$VSL,1 = VSL,2 = VL,1$$

. eq. (7)

In (7), VSL,1 and VSL,2 indicate the values of the blocked voltage by switches SL,1 and SL,2 , respectively. Moreover, the values of the blocked voltage by switches Sa and Sb are equal to

$$VSa = VSb = VR,1 + VL,1$$

eq. (8)

A new cascaded multilevel inverter can be made by series connection of n number of the H-bridge basic units. This

| S <sub>L,11</sub> | $S_{L,12}$ | $S_{R,11}$ | $S_{R,12}$ | $S_{a,1}$ | $S_{b,1}$ | $S_{L,21}$ | $S_{L,22}$ | S <sub>R,21</sub> | S <sub>R,22</sub> | $S_{a,2}$ | $S_{b,2}$ | ***  | $S_{L,n1}$ | $S_{L,n2}$ | $S_{R,n}$ | $S_{R,n2}$ | $S_{a,n}$ | $S_{b,n}$ | v <sub>o</sub>                               |

|-------------------|------------|------------|------------|-----------|-----------|------------|------------|-------------------|-------------------|-----------|-----------|------|------------|------------|-----------|------------|-----------|-----------|----------------------------------------------|

| 1                 | 0          | 0          | 1          | 0         | 1         | 1          | 0          | 1                 | 0                 | 1         | 0         | ***  | 1          | 0          | 1         | 0          | 1         | 0         | $V_{L,1}$                                    |

| 0                 | 1          | 1          | 0          | 0         | 1         | 1          | 0          | 1                 | 0                 | 1         | 0         | 244  | 1          | 0          | 1         | 0          | 1         | 0         | V <sub>R,1</sub>                             |

| 1                 | 0          | 1          | 0          | 0         | 1         | 1          | 0          | 1                 | 0                 | 1         | 0         | ***  | 1          | 0          | 1         | 0          | 1         | 0         | $V_{L,1}+V_{R,1}$                            |

|                   |            | :          |            | :         | 1         | ;          | -          | 1                 | 3                 | 1         | -         | 14.5 | :          | 1          | -         | 1          |           | 1         |                                              |

| 1                 | 0          | 1          | 0          | 0         | 1         | 1          | 0          | 1                 | 0                 | 0         | 1         | ***  | 1          | 0          | 1         | 0          | 0         | 1         | $\sum_{i=1}^{n} (V_{\tilde{L},i} + V_{R,i})$ |

| 1                 | 0          | 1          | 0          | 1         | 0         | 1          | 0          | 1                 | 0                 | 1         | 0         | ***  | 1          | 0          | 1         | 0          | 1         | 0         | 0                                            |

| 0                 | 1          | 0          | 1          | 0         | 1         | 0          | 1          | 0                 | 1                 | 0         | 1         | ***  | 0          | 1          | 0         | 1          | 0         | 1         |                                              |

| 0                 | 1          | 1          | 0          | 1         | 0         | 0          | 1          | 0                 | 1                 | 0         | 1         | ***  | 0          | 1          | 0         | 1          | 0         | 1         | $-V_{L,1}$                                   |

| 1                 | 0          | 0          | 1          | 1         | 0         | 0          | 1          | 0                 | 1                 | 0         | 1         | ***  | 0          | 1          | 0         | 1          | 0         | 1         | $-V_{R,1}$                                   |

| 0                 | 1          | 0          | 1          | 1         | 0         | 0          | 1          | 0                 | 1                 | 0         | 1         | ***  | 0          | 1          | 0         | 1          | 0         | 1         | $-(V_{L,1} + V_{R,1})$                       |

| :                 |            | :          | :          | 1         | 1         | 1          | 1          | 1                 | 1                 | 1         | 1         | 4++  | 1          | 1          | -         | 1          | 1         | 1         |                                              |

| 0                 | 1          | 0          | 1          | 1         | 0         | 0          | 1          | 0                 | 1                 | 1         | 0         | ***  | 0          | 1          | 0         | 1          | 1         | 0         | $-\sum_{i=1}^{n} (V_{L,i} + V_R)$            |

TABLE II :Output Voltage Of The Proposed Cascaded Multilevel Inverter Based On Different Switching Patterns.

| Proposed algorithm                         | Magnitude of dc voltage sources                                                                                                | N <sub>level</sub>    | Verse                                       | Numer                                            | Volunt                                   |  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------|--------------------------------------------------|------------------------------------------|--|

| First proposed algorithm $(P_i)$           | $V_{n,j} = V_{n,j} = V_{n,j}$<br>for $j = 1, 2, \dots, n$                                                                      | 4n+1                  | 2nV <sub>dc</sub>                           | 1                                                | Sel'd                                    |  |

| Second proposed algorithm $(P_2)$          | $V_{x,j} = V_{a}$<br>for $j = 1, 2, \cdots, n$<br>$V_{i,j} = 2V_{a}$<br>for $j = 1, 2, \cdots, n$                              | 6n+1                  | 3nl <sub>±</sub>                            | 2                                                | $4(2^{ml}-1) F_{ab}$ $4(3^{m}-1) F_{ab}$ |  |

| Third proposed algorithm $(P_3)$           | $V_{R,j} = V_{ab}$ $V_{L,j} = 2V_{ab}$ $V_{R,j} = V_{t,j} = 2^{j+1}V_{ab}$ for $j = 2, 3, \dots, n$                            | 2 <sup>n+2</sup> -1   | (2 <sup>set</sup> -1)V <sub>sk</sub>        |                                                  |                                          |  |

| Fourth proposed algorithm $(P_4)$          | $\begin{split} V_{A,j} &= V_{i,j} = V_{A} \\ V_{B,j} &= V_{i,j} = 3^{j-1}V_{A} \\ \text{for } j = 2, 3, \cdots, n \end{split}$ | 2×3*-1                | (3*-1)V <sub>de</sub>                       | n                                                |                                          |  |

| Fifth proposed algorithm $(P_5)$           | $V_{R,j} = V_{L,j} = V_{A}$<br>$V_{R,j} = \frac{1}{2}V_{L,j} = 2^{j-1}V_{A}$<br>for $j = 2, 3, \dots, n$                       | 3×2 <sup>n+1</sup> -7 | (3×2*-4)F <sub>ak</sub>                     | $\begin{cases} n+1 & n>1 \\ 1 & n=1 \end{cases}$ | (3×2 <sup>a-2</sup> -16) V <sub>4</sub>  |  |

| Sixth proposed algorithm $(P_a)$           | $V_{A,i} = V_{i,1} = V_{ii}$ $V_{A,j} = \frac{1}{2}V_{i,j} = 3^{-1}V_{ii}$ for $j = 2, 3,, n$                                  | 3 <sup>n+1</sup> -4   | $\left(\frac{3^{mi}-5}{2}\right)V_{dk}$     | 2n-1                                             | $(2\times3^{n+1}-10) V_a$                |  |

| Seventh proposed algorithm $(P_7)$         | $V_{R,j} = V_{i,j} = V_{ik}$<br>$V_{R,j} = V_{i,j} = 4^{1/3}V_{ik}$<br>for $j = 2, 3, \dots, n$                                | 4 <sup>n+1</sup> -1   | $\frac{2(4^*-1)}{3}V_{ik}$                  | n                                                | $\frac{2(4^{n+1}-4)}{3}F_{ab}$           |  |

| Eighth proposed algorithm $(P_8)$          | $V_{k,j} = V_{k,j} = V_{ik}$<br>$V_{k,j} = V_{k,j} = 5^{-1}V_{ik}$<br>for $j = 2, 3, \dots, n$                                 | 5"                    | $\left(\frac{5^{\circ}-1}{2}\right)V_{ab}$  | n                                                | 2(5"-1) F <sub>de</sub>                  |  |

| Ninth proposed algorithm (P <sub>0</sub> ) | $\begin{split} V_{e,a} &= 7^{-1}V_{a} \\ V_{f,a} &= 2 \times 7^{-1}V_{d} \end{split}$                                          | 7"                    | $\left(\frac{7^{\prime}-1}{2}\right)V_{de}$ | 2#                                               | 2(7"-1)**                                |  |

Table III :Proposed Algorithms And Their Related Parameters

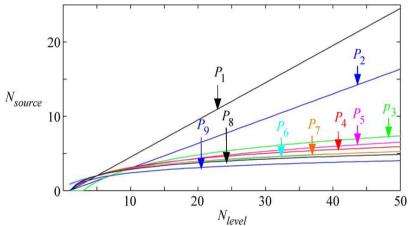

Fig. 4. Variation of Nsource versus Nlevel in the proposed algorithms.

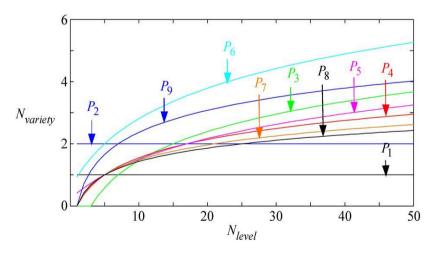

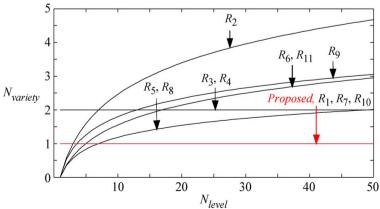

Fig. 5. Variation of Nvariety versus Nlevel in the proposed algorithms.

where VSa and VSb indicate the values of the blocked voltage by switches Sa and Sb, respectively. Therefore, the maximum amount of the blocked voltage by all of the used switches in the first unit, i.e., Vblock,1, is equal to

• Vblock,1 =

$$4(VR,1 + VL,1)$$

. eq. (9)

ISSN: 2455-4847

www.ijlemr.com // REETA-2K16 || PP. 222-233

Similarly, the maximum value of the blocked voltage by the switches in other units is calculated, and thus, the maximum amount of the blocked voltage in the proposed cascaded multi-level inverter, i.e., Vblock, is equal to

• Vblock = Vblock,1 + Vblock,2 +  $\cdots$  + Vblock,n= 4(VR,1 + VL,1 + VR,2 + VL,2 +  $\cdots$  + VR,n + VL,n ). eq. (10)

It is important to note that the existence of all voltage levels at the output is based on suitable selection of the magnitude of dc voltage sources. Thus, in order to generate all voltage levels at the output, nine different algorithms to determine the magnitude of dc voltage sources are proposed. Some of these algorithms had been presented for conventional cascaded inverters in the literature, but they could be also used in the proposed topology or any inverter and are completely based on the topology. According to each of the proposed algorithms, the number of output voltage levels (Nlevel ), the maximum amplitude of the producible output voltage (Vo,max ), the number of different voltage amplitudes of the used sources (Nvariety ), and the maximum amount of the blocked voltage by switches (Vblock ) will be different. These proposed algorithms and all of the aforementioned indexes are calculated and shown in Table III.

## COMPARING THE PROPOSED ALGORITHMS

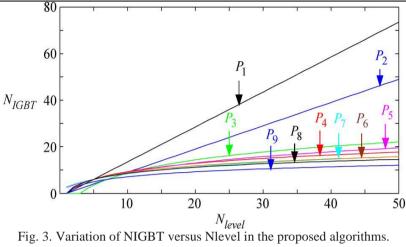

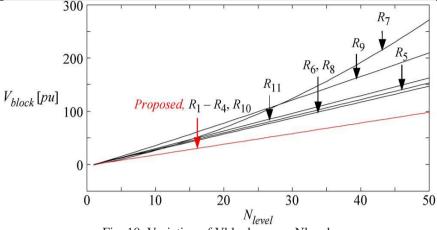

Here, the proposed algorithms are compared to each other to investigate their advantages and disadvantages. These investigations are done from several points of view such as the number of different voltage amplitudes of the used sources, the number of IGBTs, and the dc voltage sources. Fig. 3 compares the number of IGBTs in the different proposed algorithms. As it is obvious, the required numbers of IGBTs in the eighth and ninth proposed algorithms are lower than the other algorithms. As mentioned before in unidirectional switches from the voltage point of view, the number of Fig. 5. Variation of Nvariety versus Nlevel in the proposed algorithms. IGBTs is the same as the number of switches, power diodes, and driver circuits. Therefore, in the eighth and ninth proposed algorithms, the number of switches, power diodes, and driver circuits are less than the other proposed algorithms. .Fig. 4 compares the number of required dc voltage sources of the proposed topology based on the different proposed algorithms. As shown in Fig. 4, the ninth proposed algorithm needs a lower number of dc voltage sources in generating particular levels. Moreover, the first proposed algorithm requires more numbers of dc voltage sources. This feature is because of the equal magnitude of the dc voltage sources. Fig. 5 compares the number of different voltage amplitudes of the used sources in the different proposed algorithms. As it is obvious, the first proposed algorithm has a lower number of different voltage amplitudes of the used sources. In addition, the ninth proposed algorithm that needs a minimum number of IGBTs and dc voltage sources requires a high number of different voltage amplitudes of the used sources. Nevertheless, its performance is better than the other presented algorithms, except the first one. From the aforementioned comparisons, it is clear that the ninth proposed algorithm has a better performance among all the proposed algorithms.

# COMPARING THE PROPOSED TOPOLOGY WITH THE CONVENTIONAL TOPOLOGIES

The main aim of proposing the new cascaded multilevel inverter is to increase the number of output voltage levels by using a lower number of components. In order to investigate the performance of the proposed topology from the number of different voltage amplitudes of the used sources, the amount

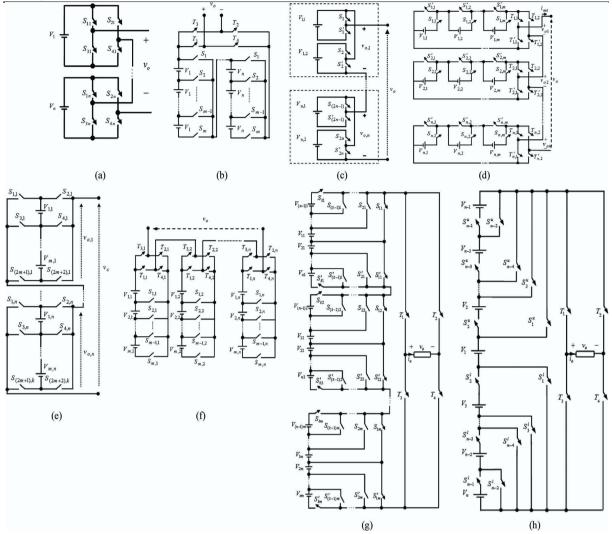

Fig. 6. Cascaded multilevel inverters.

- (a) H-bridge cascaded multilevel inverter (R1 -R2 [14], R3 [9], and R4 [10]).

- (b) Presented topology in [19] (R11).

- (c) Presented topology in [16] (R10).

- (d) Presented topology in [20] (R8).

- (e) Presented topology in [21] (R9).

- (f) Presented topology in [17] (R5).

- (g) Presented topology in [18] (R6).

- (h) Presented topology in [15] (R7).

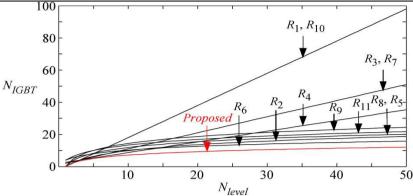

Fig. 7. Variation of NIGBT versus Nlevel.

of blocked voltage, the number of IGBTs, and the dc voltage source points of view, a comparison is done between the proposed cascaded multilevel inverter with its ninth proposed algorithm and the conventional cascaded multilevel inverters. It is pointed out that the presented conventional cascaded multilevel inverters and their different algorithms are shown by R1 –R11 in these comparisons. In [14], the H-bridge cascaded multilevel inverter with two different algorithms has been presented. This topology and its algorithms are considered by R1 and R2 in this investigation. Moreover, two other algorithms for this inverter have been presented in [9] and [10]. These algorithms are indicated by R3 and R4 , respectively. The other presented symmetric cascaded multilevel inverters in [15] and [16] are indicated by R7 and R10 , respectively. Other asymmetric topology has been also presented in [20]. In this investigation, this topology is shown by R8 . It is important to note that the unidirectional power switches from the voltage point of view are used in all of the aforementioned topologies. Moreover, several asymmetric Fig. 7. Variation of NIGBT versus Nlevel . cascaded multilevel inverters with bidirectional switches have been presented in [17]–[19] and [21]. These topologies are shown by R5 –R6 , R11 , and R8 , respectively. Fig. 6 indicates all of the aforementioned structures. Fig. 7 compares the number of the IGBTs in the proposed topology and the conventional cascaded multilevel inverters.

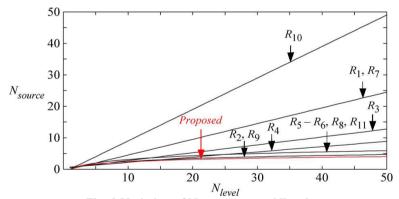

Fig. 8. Variation of Nsource versus Nlevel.

Fig. 9. Variation of Nvariety versus Nlevel.

Fig. 10. Variation of Vblock versus Nlevel.

It is obvious from Fig. 7, the number of IGBTs in the propose cascaded multilevel inverter is less than other topologies. As mentioned before, in the proposed topology, the number of switches, power diodes, and driver circuits is the same as the number of IGBTs. This comparison shows that the number of used power switches in the proposed topology is not only lower than the topologies with bidirectional switches but also less than the topologies with unidirectional ones. As a result, the proposed topology has a better feature in this point of view. Fig. 8 shows the comparison of the number of required dc voltage sources. As Fig. 8 indicates, the number of required dc voltage sources in the proposed inverter is lower than th other aforementioned topologies instead of the topologies that are indicated by R9. Fig. 9 compares the number of different voltage amplitudes of the used sources in the proposed inverter and the conventional cascaded multilevel inverters. In this comparison, the first proposed algorithm is considered. This selection is based on the obtained result from Fig. 5. It is obvious from Fig. 9 that the proposed cascaded multilevel inverter has a lower number of different voltage amplitudes of the used sources. However, this index in the proposed inverter is the same as the topologies that are shown by R1, R7, and R10. It is also important to note that he number of different voltage amplitudes of the used sources is one of the most important features in determining the cost of an inverter. By reducing this amount, the total cost of the inverter decreases. Therefore, this feature is one of the most important advantages of the proposed topology. Fig. 10 compares the magnitude of the blocked voltage by the switches in the proposed inverter and the conventional cascaded multilevel inverters. Fig. 10 shows that the proposed topology consists of the lowest amount of the blocked voltag by switches. This feature in the proposed topology is the same as the topologies that are shown by R1 -R4 and R10. This feature is known as one of the main important indexes in selecting the kinds of power switches and determines the total cost of the inverter. Therefore, if the value of the blocked voltage is reduced, the used switches have lower rating, and thus, the total cost of the inverter decreases. It is point out that all values are considered in per unit. It is clear that the proposed cascaded multilevel inverter requires a minimum number of IGBTs, power diodes, driver circuits, and dc voltage sources. In addition, in this inverter, the different voltage amplitudes of the used sources and the amount of the blocked voltage by switches are also less than the most of the conventional cascaded multilevel inverters that have been presented in the literatures, except the H-bridge cascaded multilevel inverter. These features lead to reduction of the installation space and total cost of the inverter, whereas the number of output voltage levels is increased. As a result, this inverter could be a suitable topology to replace the conventional cascaded inverters in many of applications such as drive and control of electrical machines, connection of renew- able sources, flexible alternating current transmission system devices, etc. Although the proposed inverter needs several insulated dc voltage sources, it is important to note that many of the conventional cascaded multilevel inverters, such as the presented topologies in [14], [16], and [20], require a higher number of insulated dc voltage sources. In other words, in the proposed cascaded multilevel inverter, the minimum number of insulted dc voltage sources is used.

## **EXPERIMENTAL RESULTS**

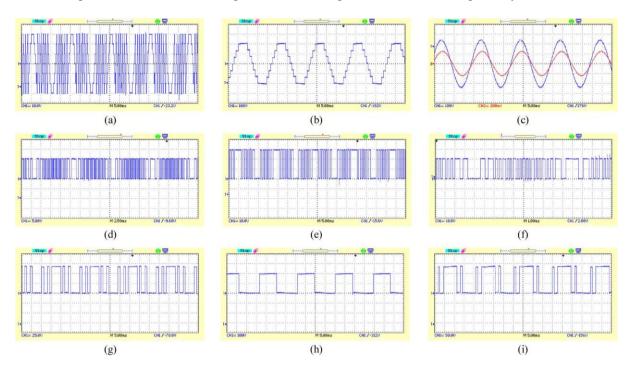

Here, the correct performance of the proposed cascaded mul-tilevel inverter in generating all voltage levels (even and odd) at the output is verified by using the experimental results of a 49-level cascaded inverter. The proposed topology consists of two series-connected developed H-bridges. The magnitude of its dc voltage sources is determined by using the ninth proposed algorithm. Therefore, the values of the used dc voltage sources in the first unit are considered to be VR1 = 10 V and VL1 = 20 V, and in the second unit, the values will

be VR2 = 70~V and VL2 = 140~V. Considering Table III, this inverter is able to generate 49 levels with the maximum amplitude of 240 V at the output. The IGBTs used on the prototype are HGTP10N40CID (with an internal antiparallel diode) with the voltage and current rating of 400 V and 10 A, respectively.

Fig. 11. (a) Output voltage waveforms of the first basic unit.

- (b) Output voltage waveforms of the second basic unit.

- (c) Output voltage and current waveforms.

- (d) Voltage on switch SR,11.

- (e) Voltage on switch Sa,1.

- (f) Voltage on switch SL,11.

- (g) Voltage on switch SR,22.

- (h) Voltage on switch Sb,2.

- (i) Voltage on switch SL,22.

The 89C52 microcontroller by ATMEL Company has been used to generate all switching patterns. In all processes of the experimental performance, the load is assumed as R-L wit R = 100  $\Omega$  and L = 55 mH. The output voltage waveforms of the first and second basic units are shown in Fig. 11(a) and (b), respectively. As shown in Fig. 11(a), the first unit has the ability of generating positive and negative levels with the magnitudes of 0, ±10, ±20, and ±30 V at the output. Moreover, according to Fig. 11(b), the second bridge generates seven levels with the values of  $0, \pm 70, \pm 140$ , and  $\pm 210$  V at the output. The output voltage and current waveforms are shown in Fig. 11(c). It is important to mention that for measuring the output current, a  $0.1-\Omega$  resistor has been used. It is obvious from Fig. 11(c) that this inverter is able to produce 49 stepped levels with the maximum output voltage of 240 V. A comparison of the voltage waveform with the current waveform shows that the current waveform is closer to the ideal sinusoidal one. This is due to the resistive-inductive load feature, which behaves as a low-pass filter. Considering the aforementioned comparison it is obvious that there is a phase different between voltage and current waveforms, which are related to the inductive characteristic of the load. As mentioned, the used power switches on the proposed cascaded multilevel inverter are as unidirectional ones from the voltage point of view; thus, in order to verify this fact, the voltage on switches SL,11, Sa,1, and SR,11 of the first bridge and SL,22, Sb,2, and SR,22 of the second bridge are indicated in Fig. 11(d)-(i). As shown in the figure, the magnitude of the standing voltage on switches are either positive or zero, and there is any negative amount on them. This fact reconfirms the existence of unidirectional power switches in this topology. As can be seen, the maximum blocking voltage by switches SR,11, Sa,1, SL,11, SR,22, Sb,2, and SL,22 are equal to 10, 30, 20, 70, 210, and 140 V, respectively. Considering the magnitude of the blocking voltage of the switches, the relations associated to the maximum blocking voltage of the switches are well confirmed.

## **CONCLUSION**

In this paper, a new general topology based on the developed H-bridge has been proposed. Nine different algorithms to determine the magnitude of the dc voltage sources of the proposed inverter are introduced. Then, a comparison between the different proposed algorithms has been done to determine the best algorithm that requires a minimum number of power electronic devices and a lower number of different voltage amplitudes of the used sources. Based on this comparison, the ninth proposed algorithm needs less number of power electronic devices, but the first proposed algorithm has a lower number of different voltage amplitudes of the used sources. The main advantage of the proposed cascaded multilevel inverter is increasing the number of output voltage levels by decreasing the number of IGBTs, power diodes, driver circuits, and dc voltage sources. In addition, in this inverter, the amount of the blocked voltage by switches is lower than the most of the presented topologies in the literatures, except the H-bridge cascaded multilevel inverter. These results are obtained from the comparison of the proposed inverter with the conventional cascaded multilevel inverters Finally, the correct performance of the proposed cascaded multilevel inverter with its new algorithm was verified by the experimental results obtained through a 49-level inverter.

## **Examples follow:**

## Journal Papers:

[1]. S. Laali, K. Abbaszades, and H. Lesani, "New hybrid control methods based on multi-carrier PWM techniques and charge balance control methods for cascaded multilevel converters," in Proc. CCECE, 2011, pp. 243–246.

#### **Books:**

- [2]. N. Farokhnia, S. H. Fathi, N. Yousefpoor, and M. K. Bakhshizadeh, "Minimisation of total harmonic distortion in a cascaded multilevel inverter by regulating of voltages dc sources," IET Power Electron., vol. 5, no. 1,pp. 106–114, Jan. 2012.

- [3]. K. Ramani and A. Krishan, "New hybrid multilevel inverter fed induction motor drive—A diagnostic study," Int. Rev. Elect. Eng., vol. 5, pt. A, no. 6, pp. 2562–2569, Dec. 2010.

- [4]. K. Ding, K. W. E. Cheng, and Y. P. Zou, "Analysis, of an asymmetric modulation methods for cascaded multilevel inverters," IET Power Electron.,vol. 5, no. 1, pp. 74–85, Jan. 2012.

- [5]. E. Babaei, M. Farhadi Kangarlu, and M. Sabahi, "Extended multilevel converters: An attempt to reduce the number of independent dc voltagesources in cascaded multilevel converters," IET Power Electron., vol. 7, no. 1, pp. 157–166, Jan. 2014.

## **Chapters in Books:**

- [6]. E. Babaei and S. H. Hosseini, "Charge balance control methods for asymmetrical cascaded multilevel converters," in Proc. ICEMS, Seoul, Korea, 2007, pp. 74–79.

- [7]. S. Laali, K. Abbaszades, and H. Lesani, "A new algorithm to determine the magnitudes of dc voltage sources in asymmetrical cascaded multilevel converters capable of using charge balance control methods," in Proc.ICEMS, Incheon, Korea, 2010, pp. 56–61.

## Theses:

[8]. E. Babaei and S. H. Hosseini, "New cascaded multilevel inverter topology with minimum number of switches," Energy Convers. Manag., vol. 50, no. 11, pp. 2761–2767, Nov. 2009.

## **Proceedings Papers:**

- [9]. J. Pereda and J. Dixon, "Cascaded multilevel converters: Optimal asymmetries and floating capacitor control," IEEE Trans. Ind. Electron.,vol. 60, no. 11, pp. 4784–4793, Nov. 2013.

- [10]. M. Manjrekar and T. A. Lipo, "A hybrid multilevel inverter topology for drive application," in Proc. APEC, 1998, pp. 523–529.

- [11]. E. Babaei, M. Farhadi Kangarlu, and F. Najaty Mazgar, "Symmetric and asymmetric multilevel inverter topologies with reduced switching devices," Elect. Power Syst. Res., vol. 86, pp. 122–130, May 2012.

- [12]. J. Napoles, A. J. Watson, and J. J. Padilla, "Selective harmonic mitigation technique for cascaded H-bridge converter with nonequal dc link voltages," IEEE Trans. Ind. Electron., vol. 60, no. 5, pp. 1963–1971, May 2013.

- [13]. J. Ewanchuk and J. Salmon, "Three- limb couple inductor operation for parallel multi-level three-phase voltage sourced inverters," IEEE Trans.Ind. Electron., vol. 60, no. 5, pp. 1979–1988, May 2013.

- [14]. S. Mekhilef, M. N. Abdul Kadir, and Z. Salam, "Digital control of three phase three-stage hybrid multilevel inverter," IEEE Trans. Ind. Informat.,vol. 9, no. 2, pp. 719–727, May 2013.

- [15]. M. F. Kangarlu and E. Babaei, "A generalized cascaded multilevel inverter using series connection of sub-multilevel inverters," IEEE Trans. Power Electron., vol. 28, no. 2, pp. 625–636, Feb. 2013.

K.BHANU CHANDAR received his bachelor degree from KMM INSTITUTE OF TECHNOLOGY AND SCIENCE, tirupathi. He is doing his master degree in SRI VENKATESA PERUMAL COLLAGE OF ENGINEERING AND TECHNOLOGY, puttur.